AUGUST 1998

Technical Information from the Hewlett-Packard Company

#### table of contents

August 1998, Volume 49, Issue 3

## **Articles**

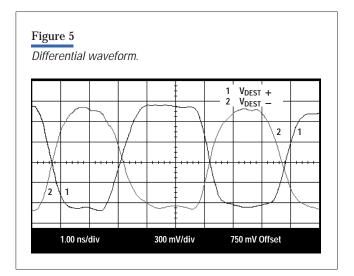

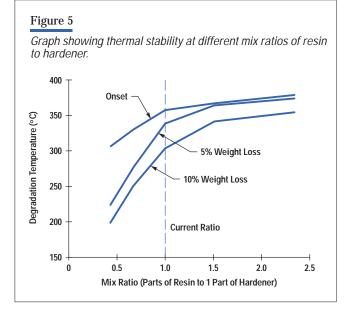

A 150-MHz-Bandwidth Membrane Hydrophone for Acoustic Field Characterization

by Paul Lum, Michael Greenstein, Edward D. Verdonk, Charles Grossman, Jr., and Thomas L. Szabo

Units, Traceability, and Calibration of Optical Instruments by Andreas Gerster

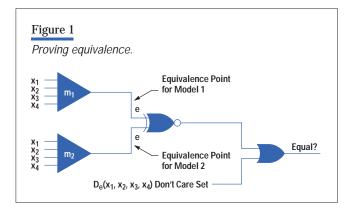

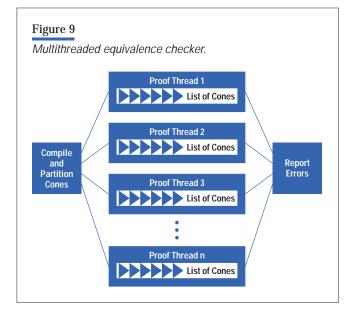

**Techniques for Higher-Performance Boolean Equivalence Verification** *by Harry D. Foster*

**On-Chip Cross Talk Noise Model for Deep-Submicrometer ULSI Interconnect** *by Samuel O. Nakagawa, Dennis M. Sylvester, John G. McBride, and Soo-Young Oh*

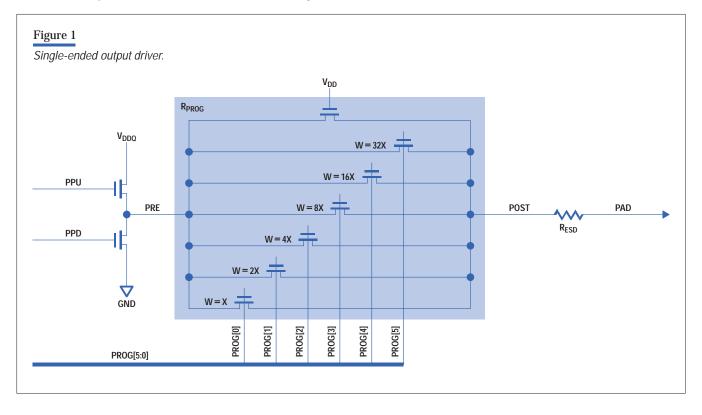

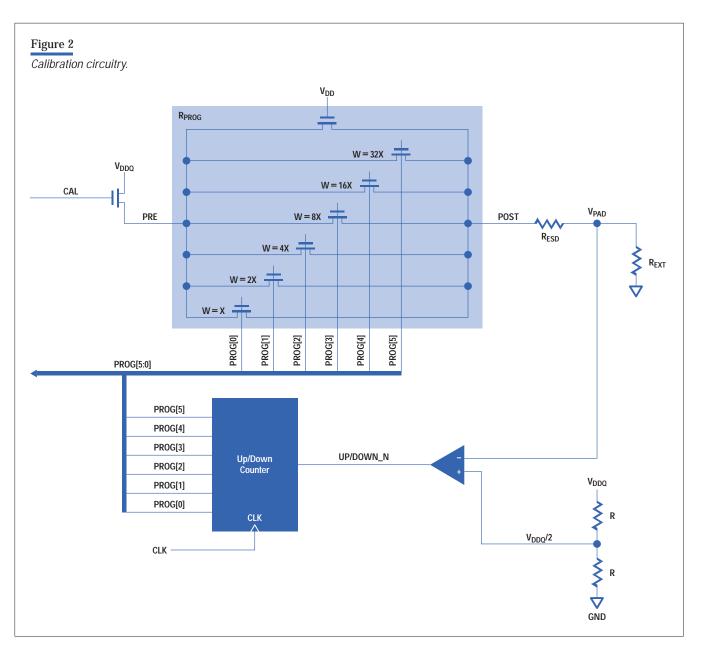

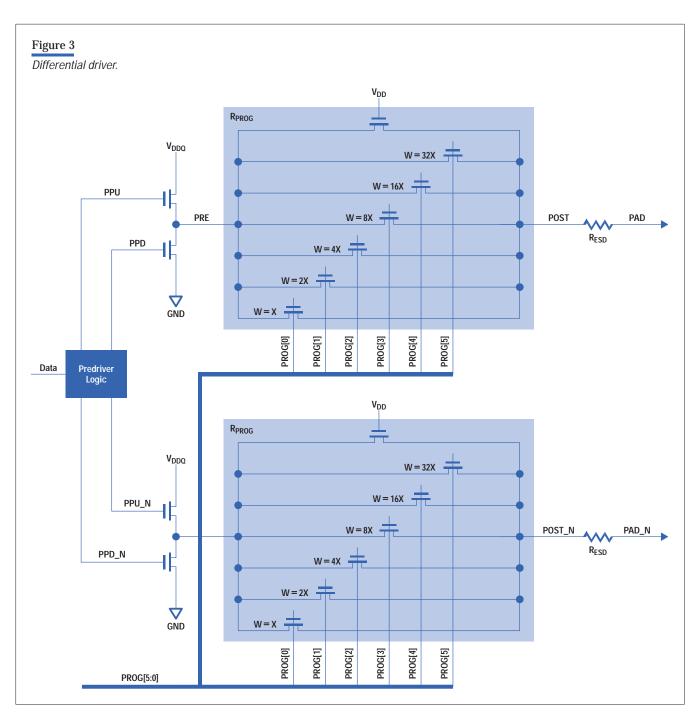

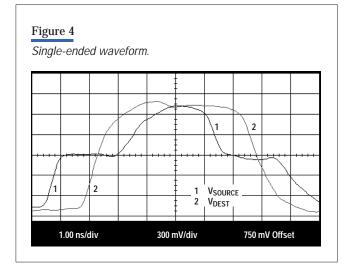

**Theory and Design of CMOS HSTL I/O Pads** by Gerald L. Esch, Jr. and Robert B. Manley

# A Low-Cost RF Multichip Module Packaging Family

by Lewis R. Dove, Martin L. Guth, and Dean B. Nicholson

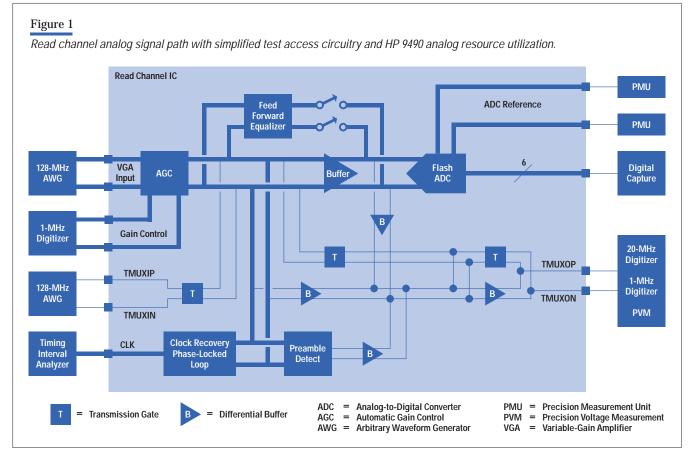

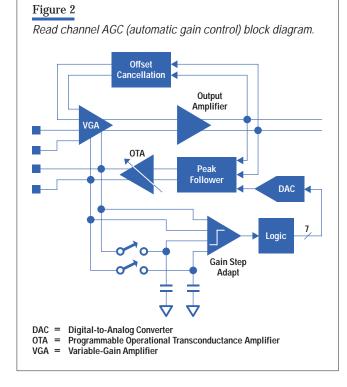

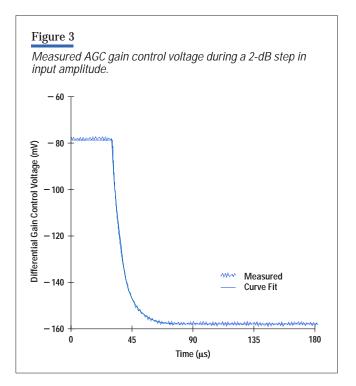

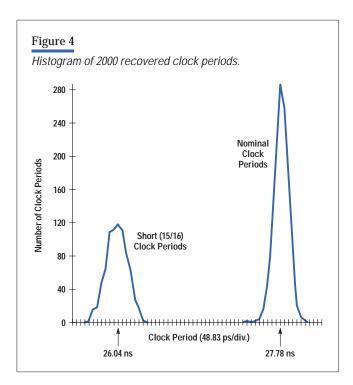

Testing with the HP 9490 Mixed-Signal LSI Tester

by Matthew M. Borg and Kalwant Singh

#### Reliability Enhancement of Surface Mount Light-Emitting Diodes for Automotive Applications

by Koay Ban-Kuan, Leong Ak-Wing, Tan Boon-Chun, and Yoong Tze-Kwan

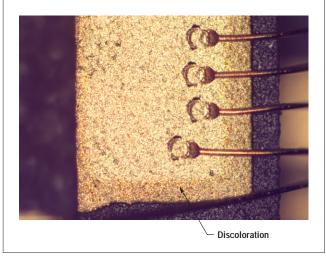

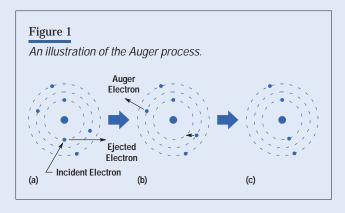

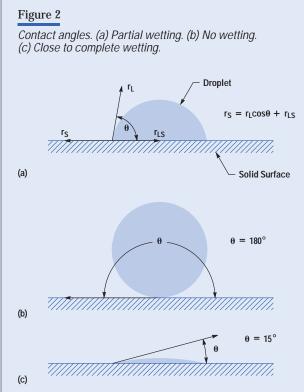

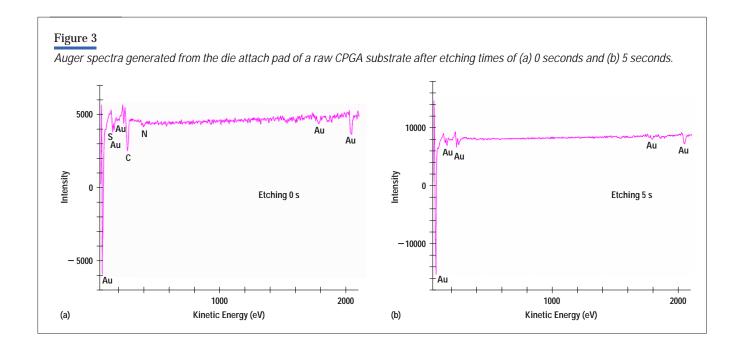

Engineering Surfaces in Ceramic Pin Grid Array Packaging to Inhibit Epoxy Bleeding by Ningxia Tan, Kenneth H. H. Lim, Bernard Chin, and Anthony J. Bourdillon

# A 150-MHz-Bandwidth Membrane Hydrophone for Acoustic Field Characterization

| Paul Lum              |

|-----------------------|

| Michael Greenstein    |

| Edward D. Verdonk     |

| Charles Grossman, Jr. |

| Thomas L. Szabo       |

To measure the beam parameters of intravascular ultrasound imaging transducers with operating center frequencies exceeding 20 MHz and beamwidths below 200  $\mu$ m, a hydrophone with a spot diameter less than 50  $\mu$ m and a bandwidth greater than 150 MHz is required. The hydrophone described in this article is a step towards meeting these requirements.

Diagnostic ultrasound imaging is used routinely in a growing number of medical applications. Hewlett-Packard manufactures a range of ultrasound imaging systems that use digital beamformers for cardiology and multipurpose imaging and mechanical beamformers for cardiology, general-purpose, and intravascular imaging.

At the heart of an ultrasound system is a transducer, an electroacoustic device that converts electrical signals into a focused mechanical wave and reconverts reflected mechanical echoes from organs and tissue for subsequent real-time image construction. The transducer is a resonant device that has a bandpass filter frequency response. Currently available transducers have a center frequency in the range of 2 to 30 MHz. A phased array of individual transducers, typically consisting of 30 to 300 elements, is electronically focused and steered to provide a beam with the dimensions desired for a selected medical application.

Current trends in imaging are to the following higher-frequency applications:

- Intravascular imaging for plaque detection in blood vessels such as the coronary arteries

- Contrast-agent-assisted harmonic frequency imaging to view blood flow and perfusion in the heart

6

- Small parts imaging for near-surface high-definition examination of burn injuries, skin lesions, and cancers

- Laparoscopic surgery (ultrasound-guided interventional surgery)

- Ocular imaging (high-resolution visualization of anomalies and repairs of the eye).

These trends pose challenges in the characterization of the transducers used. By law, ultrasound imaging system manufacturers are required to measure the acoustic output of their systems at the transducer. To characterize the acoustic waves of these systems, small calibrated transducers called hydrophones are used. To avoid altering the acoustic fields they are measuring, hydrophones must be as nonperturbing as possible and must far exceed the bandwidth and the spatial resolution of the transducers being measured. This paper describes a new membrane hydrophone that provides the performance needed for these exacting applications.

The hydrophones presently used in the industry have - 3-dB bandwidths of 15 to 20 MHz and effective spot sizes of 500 µm. They are appropriate for characterizing acoustic medical imaging transducers up to about 7 MHz. However, even transducers at these frequencies generate, through nonlinear propagation effects in water, higher harmonics that extend in frequency beyond the -3-dB bandwidths of the available hydrophones. To fully characterize a transducer, detection of the fifth harmonic is needed. Furthermore, there are new ultrasonic imaging modalities, such as intravascular ultrasound (IVUS) in the 30-MHz frequency range with 50-µm wavelengths. These transducers cannot be adequately characterized by 15-to-20-MHz-bandwidth hydrophones. (IVUS gives a cross-sectional view of the interior of coronary arteries to assess coronary atherosclerosis.)

Peak pulse parameters calculated from hydrophones with inadequate frequency response show large errors. Hydrophones with effective spot sizes that are too large underestimate the critical parameter of peak pressure because they average the pressure over the hydrophone's active area.

The IEC<sup>1</sup> and NEMA<sup>2</sup> standards regulate the characterization of medical ultrasound transducers by specifying the parameters of the hydrophones used to measure these transducers. The required effective spot diameter is 50  $\mu m$  for a hydrophone to measure a 30-MHz IVUS transducer with a typical 1-mm aperture and a transducer-to-hydrophone range of less than 2 mm. For more details on transducer characterization, see the box on page 8.

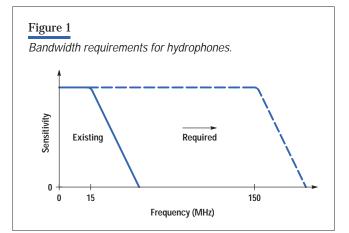

In view of these considerations, there is an important need for hydrophones capable of characterizing transducers with frequency components in the range of 150 MHz and a spatial resolution of typically less than 50  $\mu$ m. This is illustrated in **Figure 1**, which is a plot of sensitivity as a function of frequency for both existing and required hydrophones.

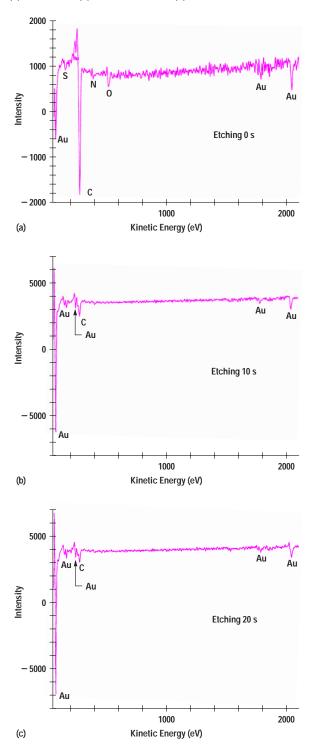

This article describes the modeling, fabrication, and initial characterization of a membrane hydrophone capable of meeting these more exacting bandwidth and spatial requirements. The hydrophone is fabricated from a 4-µm-thick film of spot-poled\* PVDF-TrFE piezoelectric polymer material. It has on-membrane electronics, a -3-dB bandwidth in excess of 150 MHz, and a measured effective spot diameter of less than 100 µm.<sup>3</sup>

\* Poling refers to the process of aligning the directions of the ferroelectric domains in a ferroelectric material so that a net polarization occurs. The polymer material used for the hydrophone comes with random ferroelectric polarization. By applying an electric field at an elevated temperature we can rotate the directions of the individual polarization vectors so that they are all aligned along the electric field direction. The higher temperature lowers the work required. When the material returns to room temperature the domains stay aligned, thus creating an active region. Spot-poling is poling confined to selected areas.

## The Hewlett-Packard Medical Products Group Acoustic Output Measurement Laboratory

The control and display of acoustic output have important performance and quality implications for medical diagnostic ultrasound equipment. The acoustic output of these devices should be optimized to provide image quality sufficient for a clinician to make a diagnosis, while at the same time, must be limited to U.S. Food and Drug Administration (FDA) approved levels. The FDA has set limits for acoustic output, and requires reporting of maximum output levels before marketing these devices and as part of the device labeling. Output measurements on production units are performed to ensure manufacturing process control and to establish compliance with FDA Quality System Regulations (QSR). Recognizing that measurement of acoustic output is an essential part of the design, manufacture, and marketing of this equipment, the HP Medical Products Group (MPG) in 1985 established a dedicated, state-ofthe-art, acoustic output measurement laboratory at Andover, Massachusetts.

Laboratory Description. The laboratory has instruments required to perform measurements of acoustic pressure, intensity, frequency, and power in the range of 1 to 20 MHz, and is staffed by managers, support engineers, and highly skilled measurement technicians.

The primary measurement system used to measure pressure, intensity, and frequency consists of a water tank, hydrophone, motorized precision positioning system, high-speed sampling oscilloscope, system controller, and associated measurement software. The positioning system provides repeatable positioning of the acoustic beam relative to the hydrophone in the water tank and allows automatic scanning of the acoustic field. The oscilloscope captures the hydrophone output and transfers the sampled data to the system controller for parameter computation (pressure, intensity, frequency).

A radiation force balance is used to measure total acoustic power. This device consists of a small sound-absorbing target attached to one arm of a microbalance suspended in a water column. To perform a power measurement, the source transducer is coupled to the water column and the acoustic beam is directed at the target. The resulting force on the target, as measured by the microbalance, is proportional to the total acoustic power.

The methodology for performing these measurements conforms to those specified in the NEMA UD-2 Acoustic Output Measurement Standard, the NEMA/AIUM Standard for Real-Time Display of Thermal and Acoustic Output Indices on Diagnostic Ultrasound Equipment, and international standards.

Laboratory Mission. The laboratory's mission is fourfold. The first mission is to support the development of new ultrasound products. Before clinical studies, measurements are performed on prototype equipment to characterize the acoustic field, and maximum acoustic output is verified to be at or below FDA approved limits for pressure and intensity. Later, after more systems are manufactured, output control and display are optimized and validated, and additional measurements are performed to establish the output variability of newly designed products. Finally, production test protocols and test limits are established.

The second mission is to collect acoustic output data required for regulatory labeling. This includes collection of data for premarket notification and other international requirements.

The third mission is to support manufacturing engineering. The laboratory is responsible for addressing all aspects of acoustic output measurement related to FDA-GMP and ISO requirements, including the establishment of production test procedures and test limits and calibration and maintenance procedures of unique test equipment.

Finally, the laboratory is committed to advancing ultrasonic exposimetry, acoustic output measurement science, and associated measurement standards. The laboratory provides a real-world environment for the development of new measurement devices, such as the HP wideband hydrophone described in the accompanying article, and laboratory engineers are actively involved in national and international measurement standards committee work (NEMA, AIUM, IEC, etc.).

To accomplish these missions, the laboratory maintains close, cooperative working relationships with MPG's ultrasound product design team as well as MPG's manufacturing engineering and regulatory staffs.

Charles Grossman, Jr., Thomas L. Szabo, Kathleen Meschisen, and Katharine Stohlman Imaging Systems Division

#### Acoustics

f

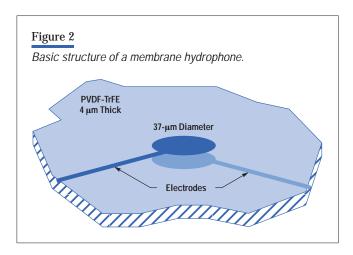

The basic structure of a membrane hydrophone is shown in **Figure 2**. Here, a portion of a thin membrane is shown with an electrode and a trace on each side of the membrane. The center frequency is inversely proportional to the thickness of the piezoelectric membrane. The spatial resolution of the hydrophone improves as the diameter of the electrode decreases, and the sensitivity and bandwidth are determined by the piezoelectric coupling of the membrane. The active area of the hydrophone is determined by the overlap of the top and bottom electrodes. In practice, one of the electrodes is extended over a large portion of the membrane to serve as a ground plane.

Acoustic modeling was used to characterize the effects of spot size, film thickness, mass loading from the thin-film electrodes, and directional sensitivity (directivity). The major differences in the properties of the piezoelectric polymer materials between the copolymer PVDF-TrFE used here and the more commonly used PVDF are the increased dielectric constant, the increased effective coupling constant, and the decreased electrical loss tangent of the copolymer.

The thickness-mode resonant frequency, f<sub>o</sub>, of the membrane hydrophone is given by:

$$C_0 = \frac{c}{2t},\tag{1}$$

where c is the acoustic velocity and t is the thickness of the membrane. This relation comes from the requirement that the thickness dimension of the membrane film must be a half wavelength. In general, it is important to have the thickness resonance of the membrane beyond the

#### Figure 3

measurement range to maximize the flatness of the sensitivity. A 4- $\mu$ m film satisfies this requirement by placing the thickness resonance frequency at 150 MHz. The thickness resonance is also affected by the mass of the metal electrodes. For a 4- $\mu$ m membrane, conventional 3000Å electrodes degrade the peak frequency of the sensitivity and the fractional bandwidth. A choice of 1000Å for the electrode thickness is a good compromise between a corrosion-resistant electrode with adequate conductivity and adequate bandwidth.

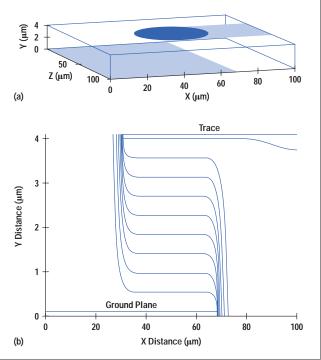

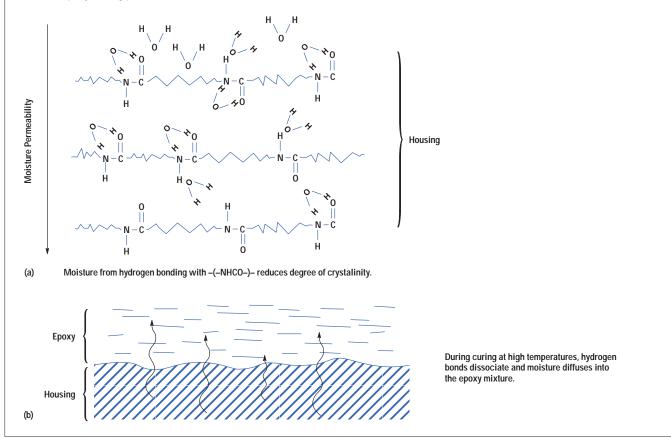

#### **Electrostatic Fringe Fields**

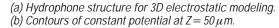

During the spot-poling process, the applied electric fields fringe beyond the edge of the spot electrode and can pole areas of the piezoelectric polymer beyond the intended spot electrode. Electrostatic field modeling was used to model the electrical field patterns to estimate the extent of the fringe field. Voltages on the three-dimensional structure are specified and Poisson's equation is solved iteratively. The geometry of the model is shown in **Figure 3a**. A 37-µm-diameter electrode spot and trace are patterned over a semi-infinite ground plane. These are on opposite sides of a 4- $\mu$ m-thick polymer film. In **Figure 3b**, 10% incremental contour plots of the electrical potential are shown for a central cross section in the X-Y plane, through the trace at the top, the polymer film, and the bottom ground plane. An additional 10  $\mu$ m is poled at greater than 50% of the maximum potential on the electrode. Therefore, this model predicts a larger total active diameter of about 50  $\mu$ m.

#### **Electrical Matching**

The effects of spot size and film thickness are seen by approximating the electrical impedance by capacitive reactance. This reactance is:

$$Z = \frac{-j}{2\pi f_o C_o} = \left(\frac{-j}{c\epsilon}\right) \left(\frac{2t}{\pi D}\right)^2,$$

(2)

where t is the thickness, D is the diameter of the spot,  $\epsilon$  is the clamped dielectric constant, and c is the speed of sound in the membrane. Thus the electrical impedance of the membrane hydrophone increases with the square of the membrane thickness and inversely with the square of the spot diameter. For a 4-µm-thick membrane with a 37-µm-diameter spot, Z is 100,000 ohms. This high impedance presents a challenge for matching the transducer to the 50-ohm impedance of the cable used to connect the hydrophone to an oscilloscope.

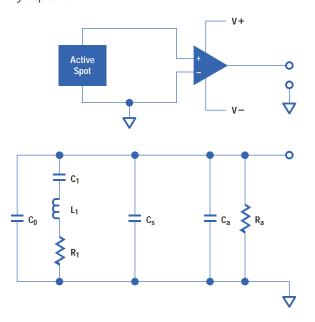

Figure 4 shows the schematic diagram and equivalent circuit for a membrane hydrophone with an adjacent amplifier. At the far left of the overall equivalent circuit is the equivalent circuit for the piezoelectrically active area resonator. This circuit yields two conditions for resonance. A series resonance condition exists when C<sub>1</sub>, L<sub>1</sub>, and R<sub>1</sub> resonate to produce an electrical impedance minimum, and a parallel resonance condition exists when the C<sub>1</sub>-L<sub>1</sub>-R<sub>1</sub> branch is inductive and tunes with C<sub>0</sub> to produce an impedance maximum. In the middle, C<sub>s</sub> represents the stray capacitance of the connecting electrode. The adjacent amplifier is represented by a capacitance C<sub>a</sub> and a real impedance Ra. Not shown is the 50-ohm coaxial cable that connects the amplifier output to additional electronic circuitry. On-membrane electronics are used to avoid corrupting the frequency characteristics and to match a 50-ohm cable properly.

#### Figure 4

Schematic and equivalent circuit for the membrane hydrophone.

#### **Spatial Resolution**

The spatial resolution of a hydrophone is determined by the effective spot size. The effective spot size is in turn determined by the geometric spot size and other electrical and acoustic factors. If the spot size is significantly larger than the size of the acoustic beam being measured, spatial averaging occurs (a hydrophone measures pressure, not energy). Averaging by the hydrophone results in overestimating the size of the beam and underestimating the absolute pressure levels of the beam. These two effects will be illustrated and discussed later in this article for both largediameter and small-diameter hydrophones.

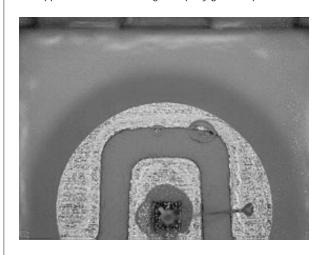

#### **Fabrication**

The fabrication of a membrane hydrophone begins with the raw PVDF-TrFE film in a roll form. An evaporator is used to deposit metal electrodes onto both sides of the film. Shadow masks establish the electrode patterns. One side is patterned for the active spot electrode and the on-membrane electronics connections. The other side is patterned for the ground plane. Alignment of the ground plane relative to the spot electrode is necessary to correctly establish the overlap of the spot electrode.

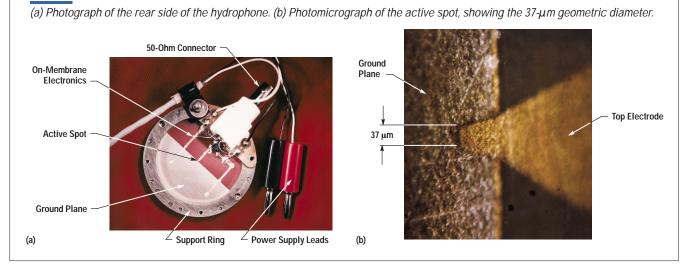

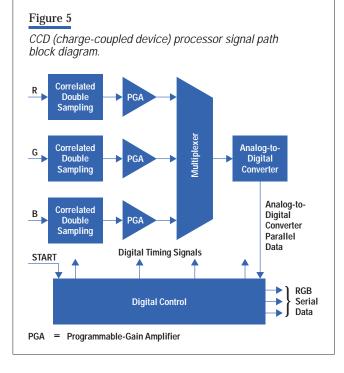

#### Figure 5

The membrane is then mounted onto a ring support structure. In its raw state, as received from the vendor, the piezoelectric PVDF-TrFE film is unpoled with unaligned ferroelectric domains. To align these domains and create the piezoelectric active area, the film is spot-poled at a temperature of 130°C and an electric field strength of 70V/ $\mu$ m.

A film thickness of 4  $\mu$ m and a spot size of 37  $\mu$ m result in a device with an electrical impedance of about 100 kilohms. Such a hydrophone is not well-matched to the 50-ohm cable typically used to connect the hydrophone to an oscilloscope input. This substantial electrical impedance mismatch issue is resolved by mounting a wideband, lowdistortion buffer amplifier directly on the membrane. The selected amplifier, a surface mount device, has a frequency response that is flat within  $\pm 1$  dB from dc to 500 MHz and an input impedance on the order of 450 kilohms. To avoid distorting the acoustic field, the amplifier is surface mounted directly onto the membrane at a distance of 10 mm from the spot electrode. The electronics are encapsulated with a cast backing of silicone resin that also acts to protect the fragile 4-µm-thick film. After the backing is cured, the hydrophone is characterized.

A photograph of the rear surface of the hydrophone is shown in **Figure 5a** with several of the key structures highlighted. Normally the back side of the hydrophone is encapsulated in a silicone gel to support the membrane and protect the electronics from the water environment. The membrane is stretched taut over the 60-mm diameter stainless steel support ring. The ground plane can be seen on the bottom left half of the membrane. The active spot is at the end of the trace pointing toward the center of the membrane. The on-membrane electronics are located in the upper right portion of the photo, with the two power supply leads shown on the right side of the photo. The hydrophone is terminated into a standard BNC 50-ohm coaxial connector. Figure 5b is a photomicrograph of the active area. Here the top surface electrode is seen on the right as it tapers down to a 37-µm diameter. The ground plane is located in the left half of the picture, under the piezoelectric film, just overlapping the 37-µm-diameter spot. The spatial overlap of the top electrode and the ground plane defines the active spot, once it has been poled.

#### Bandwidth

One of the key design goals is a -3-dB bandwidth of at least 150 MHz. Several potential methods for measuring the bandwidth include calibration against a known standard hydrophone, interferometry, reciprocity, and the nonlinear distortion method. The first three are generally accepted calibration methods but are currently limited to a maximum frequency of 50 MHz. The nonlinear distortion method, although not considered a standard method, is capable of measurements above 150 MHz, and was chosen to evaluate the new hydrophone. In the nonlinear distortion method, a source transducer is used to produce nonlinear effects in the water propagation medium. In a fully developed shock wave, such as the familiar one generated by a jet airplane, a classic N wave, or N-shaped waveform, may be formed. The N wave gets its name from its very steep compressional rise time and its more gradual rarefaction fall time. As the waveform propagates, a shock front develops, which generates new frequency components not present in the original waveform. The frequency spectrum of an ideal N-shaped shock wave has frequency harmonics at multiples n of the fundamental, where  $n = 1, 2, 3, ..., \infty$ . In the classic N wave, each harmonic amplitude falls off as 1/n. Perfect N waves are rarely achieved in the fields of medical ultrasound transducers because of diffraction phase effects in the beam. However, nonlinear distortion methods can still provide an extremely broadband signal to aid in the evaluation of hydrophone bandwidth.

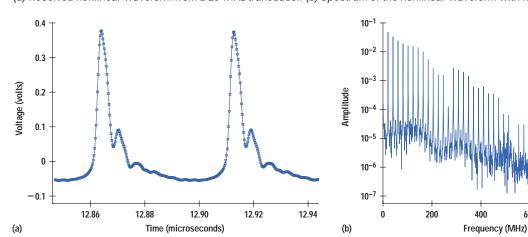

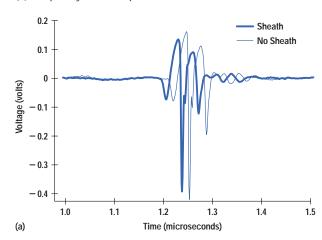

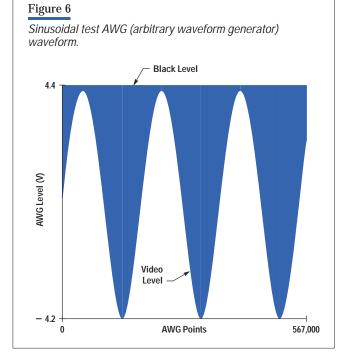

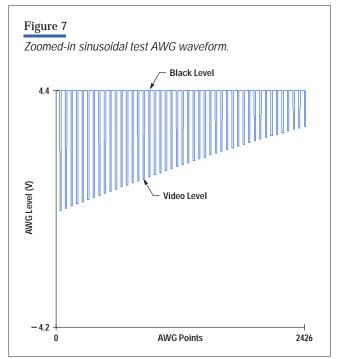

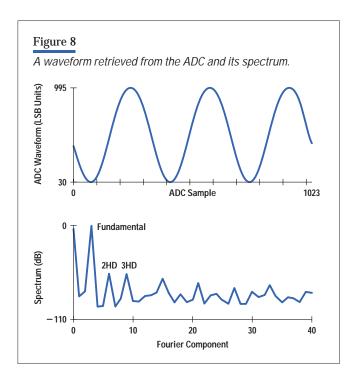

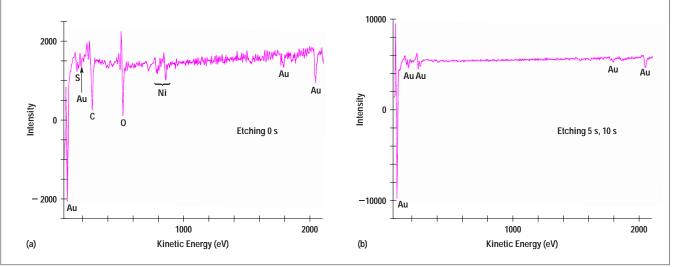

An imperfectly shaped N waveform is shown in **Figure 6a**. This waveform is from a 20-MHz, 6.4-mm-diameter transducer excited in a tone-burst mode, as recorded by an HP 54720A digital oscilloscope and an HP 54721A plug-in amplifier with a 1-GHz analog bandwidth. The hydrophone is placed at the focal plane distance of 19 mm. In the focal plane, the intensity is sufficient to exploit the nonlinear properties of water to generate useful nonlinear distortion. The waveform exciting the transducer is a 20-MHz sinusoidal tone burst. Because of the nonlinear properties of the water propagation medium, the positive compressional half-cycles exhibit very fast rise times, while the negative rarefaction half-cycles exhibit slower fall times. The higher frequencies generated this way do not suffer significant propagation-related attenuation because they are generated right where they are detected.

The -3-dB bandwidth can be estimated from the sharp compressional portion of this waveform. From the 10%-to-90% rise time, a bandwidth of 150 MHz is calculated. The related frequency spectrum is shown in **Figure 6b**. The harmonics from the fundamental at  $\sim$  20 MHz up to  $\sim$  800 MHz can be seen. The peaks, corresponding to the harmonics at 20-MHz intervals, show the extent of the nonlinear distortion of the waveform. Without the nonlinear distortion, most of the energy would be located at the fundamental frequency of 20 MHz. At  $\sim$  700 MHz, the -3-dB bandwidth of the buffer amplifier limits the measured frequency response of the hydrophone. Thus, this hydrophone can detect acoustic frequency components out to at least 800 MHz.

The superior bandwidth of this membrane hydrophone relative to hydrophones currently in use can be demonstrated by performing comparative measurements on acoustic fields generated by medical diagnostic ultrasound equipment. Comparative waveform measurements were made with a Hewlett-Packard SONOS 2500 diagnostic imaging system and a 5-MHz phased array transducer as the source. Two hydrophones were used to measure the acoustic waveform at focus. A calibrated reference

#### Figure 6

(a) Received nonlinear waveform from a 20-MHz transducer. (b) Spectrum of the nonlinear waveform with harmonics up to 800 MHz.

800

1000

600

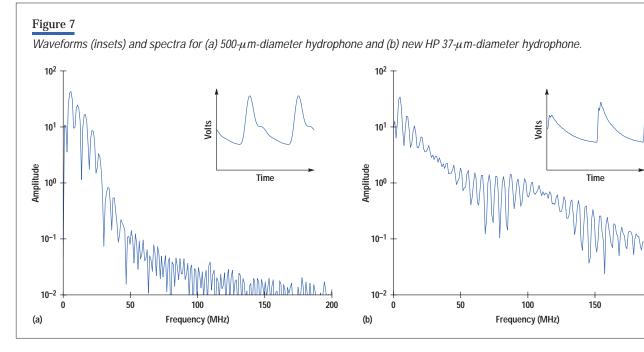

membrane hydrophone with a 500-µm spot diameter on a 25-µm-thick bilaminar PVDF membrane was compared with the new HP high-frequency membrane hydrophone with a 37-µm spot on a 4-µm-thick membrane. Figure 7a shows the frequency spectrum using the 500-µm-diameter hydrophone, and the inset shows the measured nonlinear waveform. The spectrum shows the fundamental at 5 MHz and three harmonics at 10, 15, and 20 MHz. Figure 7b shows the frequency spectrum using the new HP 37-µmdiameter hydrophone, and the inset shows the respective waveform that has greater detail and a sharper rise time because of the greater bandwidth. The spectrum shows the fundamental at 5 MHz and the subsequent 40 harmonics out to 200 MHz. This frequency data correlates well with the spectra shown in Figure 6, given the lower excitation frequency of the SONOS system.

#### Sensitivity

The sensitivity of a membrane hydrophone can be determined by two fundamental parameters. The first is the thickness resonance of the membrane film. The second is the response determined by the electrical and piezoelectric properties of the material. For a hydrophone the receive voltage sensitivity, M, is given by the ratio of the developed voltage to the incident acoustic pressure, that is, M = V/P.

Although the open-circuit voltage sensitivity is the most direct measure of the sensitivity of a hydrophone, it is difficult to measure with the new HP hydrophone and its required on-membrane amplifier. Consequently, the loaded-end-of-cable sensitivity,  $M_L$  (relative to 1 V/MPa), was measured and found to be  $-23\pm2$  dB, within -1.5 dB of the reference 500- $\mu$ m-diameter hydrophone. This comparison was done with the reference hydrophone configured with a 6-dB external amplifier and the wideband hydrophone driving an external 25-dB amplifier. In each case the circuits are optimally tuned with the external amplifiers in place. Although sensitivity calibration measurements are needed out to 150 MHz, there is not yet a satisfactory calibration procedure for the required range.

200

#### Effective Spot Size

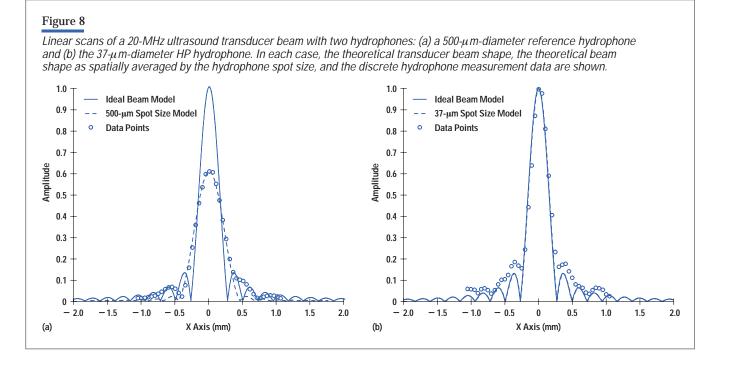

When the hydrophone diameter is significantly larger than the beam it measures, spatial averaging occurs. To compare the spatial resolution of the HP high-frequency hydrophone with a reference hydrophone with a 500-µm spot size, the tightly focused beam of a 20-MHz, 6.4-mm-diameter transducer was measured by both hydrophones close to the focal plane. The measured beam of this transducer at its focal length is close to the ideal predicted by theory provided that a sufficiently small hydrophone is used to make the measurement. The measured field can be modeled to a good approximation as the spatial average of the theoretical field over the hydrophone area. Because of radial symmetry, the area averaging simplifies to a running mean across the theoretical beam.

Measured beamwidths for the two hydrophones are compared to theoretical calculations of the spatially averaged and unaveraged beamwidths in **Figure 8**. In **Figure 8a** the data from the 500-µm reference hydrophone is shown, and the comparable data for the HP hydrophone is given in **Figure 8b**. These curves demonstrate that the reference hydrophone underestimates the on-axis pressure at the beam peak by 40% and overestimates the beamwidth by 50%, whereas the new HP high-frequency hydrophone provides a faithful replica of the beam shape and pressure.

Angular measurement techniques can also be used to estimate the effective spot size of a hydrophone. In the angular response method, the hydrophone is swept through an arc about the reference transducer. In this way, directional response can be measured and used to estimate the effective diameter. In this method the actual beamwidths at -3 dB and at -6 dB are compared to those expected from theory. From the theoretical beamwidth, for a given frequency, the effective hydrophone spot diameter can be inferred from the beamwidth data. The same 20-MHz focused transmitter was used to perform a directivity

measurement. The resulting measured half angles, when applied to the theoretical model, indicate a spot diameter upper bound of 100  $\mu$ m for the device measured.

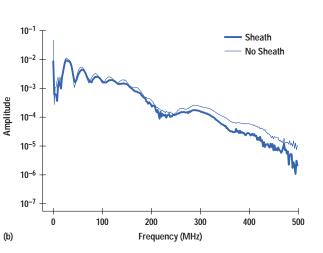

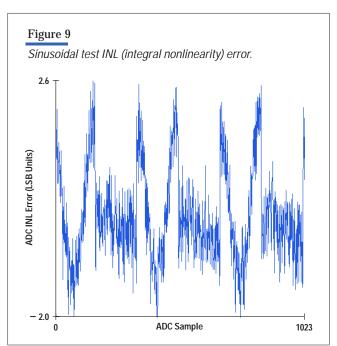

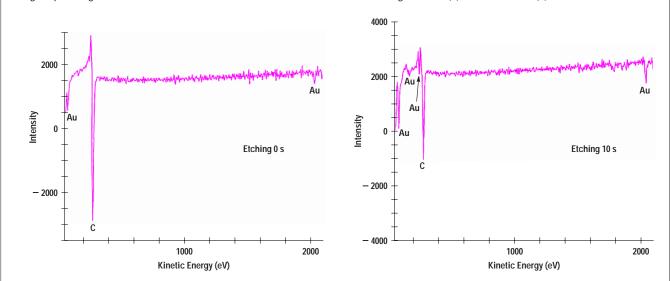

#### Intravascular Ultrasound Application

As an example of the application of this new hydrophone, a 30-MHz IVUS catheter transducer excited by an HP IVUS system under normal system settings was characterized. In use, a stationary sheath is used to protect the intimal lining of the blood vessel (one monolayer of cells thick) from the rotating catheter and transducer. The sheath both attenuates and focuses the beam. In Figure 9a, the waveform is shown as received by the hydrophone after a 1.9-mm path in water. The hydrophone was carefully placed on the axis of sound propagation. The thick line is the waveform with the 110-µm-thick polymer sheath, and the thin line is the waveform without the sheath. The beam that is focused by the sheath arrives at the hydrophone earlier. The disparity in the rise and fall times of these signals is an indication that nonlinear distortion has developed in the water medium. The frequency spectra of these waveforms in Figure 9b indicate the presence of nonlinear distortion both with a sheath and without a sheath. There are frequency components of this waveform out to at least 150 MHz, which cannot be measured by a conventional 20-MHz-bandwidth hydrophone.

#### Figure 9

HP membrane hydrophone measurements of nonlinear data from a 30-MHz IVUS catheter. (a) Time-domain waveforms. (b) Frequency-domain spectra.

#### Summary

With the increasing use of intravascular ultrasound imaging transducers with operating center frequencies exceeding 20 MHz and beamwidths below 200  $\mu$ m, smaller-spot-size and higher-frequency hydrophones are needed. Characterizing transducer acoustic pressure fields according to the AIUM/NEMA standards requires a hydrophone with a spot diameter less than 50  $\mu$ m and a bandwidth greater than 150 MHz. The hydrophone described in this article is a step towards meeting these requirements.

Acoustic modeling was performed to provide a general guideline for selecting the membrane thickness, electrode diameter, electrode conductor metal thickness, electrode interconnect lead length, and placement of the amplifier. Fabrication of the hydrophone required characterization of the material, electrode patterning, spot poling, and assembly. The nonlinear distortion method was used to evaluate the bandwidth. Directivity measurements were used to determine an upper limit for the effective spot diameter. The substitutional method was used to evaluate the hydrophone sensitivity up to 20 MHz. As an example of the capability of the hydrophone, the on-axis signal from a 30-MHz IVUS transducer in water was characterized.

The result of this work is an acoustic hydrophone fabricated on a 4- $\mu$ m-thick membrane film of PVDF-TrFE, having an effective active spot less than 100  $\mu$ m in diameter, an on-membrane buffer amplifier within 10 mm of the active spot, and a loaded end-of-cable sensitivity of - 23 dB relative to 1V/MPa in the range 5 to 20 MHz. Additional characterization is needed to determine the absolute hydrophone response in the range of 20 to 150 MHz, and to measure the effective spot size more accurately. Further details on this hydrophone and a more complete set of references are given in reference 3. This hydrophone has been licensed to an external vendor for commercialization, and is expected to be available in the spring of 1998.

#### Acknowledgments

The authors would like to acknowledge Belinda Kendle for help with hydrophone fabrication, Said Bolorforosh for many useful discussions, Henry Yoshida for the poling system, Jerry Zawadzki for numerous fixtures, Pete Melton and Kate Stohlman for their continual support and encouragement, and Paul Magnin for his consistent level of support.

#### References

1. *Measurement and Characterization of Ultrasonic Fields Using Hydrophones in The Frequency Range 0.5 MHz to 15 MHz*, IEC 1102:1991.

2. Acoustic Output Measurement Standard For Diagnostic Ultrasound Equipment, NEMA Standards Publication No. UD 2-1992, National Electrical Manufacturers Association, 2101 L Street, N.W. Washington, D.C. 20037.

Paul Lum

Paul Lum is a member of the technical staff of the analytical medical labo-

ratory of HP Laboratories, specializing in medical sensors, actuators, transducers, and instrumentation. With HP since 1977, he holds an MS degree in electrical engineering and computer science from the University of Santa Clara. A native of San Francisco, he is married and has two children.

Michael Greenstein Michael Greenstein received his PhD degree in experimental solid-state

physics from the University of Illinois Urbana-Champaign in 1981 and joined HP Laboratories in 1982. He is currently a project manager for diagnostic sensors and devices. His work has resulted in 18 patents and 26 publications. Born in Oakland, California, he is married, has a daughter, raises bonsai trees, and plays soccer.

#### Edward D. Verdonk

Ed Verdonk is a member of the technical staff of the analytical medical

laboratory of HP Laboratories, specializing in ultrasound imaging. He received his PhD degree in physics in 1992 from Washington University of St. Louis and joined HP in 1993. He is married, has a daughter, and comes from Edmonton, Alberta, Canada.

#### Charles Grossman, Jr. Charlie Grossman is a manufacturing development engineer at the HP

Imaging Systems Division and supports the Acoustic Output Measurement Laboratory. He joined HP in 1979 after ten years in circuit design with GTE. His BSEE degree (1969) is from the State University of New York at Buffalo. Born in Munich, Germany, he enjoys photography and travel.

#### Thomas L. Szabo

Tom Szabo joined HP in 1981 after 12 years of research activities with the

U.S. Air Force. A senior R&D engineer with the HP Imaging Systems Division, he is involved in transducer array design, beamforming, and acoustic output characterization. He received his PhD degree in physics from the University of Bath (UK) in 1993. He has published 65 papers and his work has resulted in three patents. A native of Budapest, he is married, has a son, and enjoys photographing megalithic sites and gargoyles and training cats to do tricks.

3. P. Lum, M. Greenstein, C. Grossman, and T. Szabo, "High-Frequency Membrane Hydrophone," *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, Vol. 43, no. 4, July 1996, pp. 536-544.

# Units, Traceability, and Calibration of Optical Instruments

Andreas Gerster

This article presents a short and comprehensive overview of the art of units measurement and calibration. Although the examples focus on optical instruments, the article may be of interest to anyone interested in metrology.

Let increasing number of companies using quality systems, such as the ISO 9000 series, explains the growing interest in the validation of the performance of measurement instruments. For many customers it is no longer sufficient to own a feature-rich instrument. These customers want to be sure that they can test and measure in compliance with industrial and legal standards. Therefore, it is important to know how it can be guaranteed that a certain instrument meets specifications.

This article is intended to give an overview of the calibration of optical power meters and other optical instruments at HP. Along with the specific instruments, common processes and methods will be discussed. The first section will deal with some aspects of the theory of measurement. Then, processes and methods of calibration and traceability will be discussed. These first two sections give a general and comprehensive introduction to the system of units. Finally, the calibration procedures for certain HP optical instruments will be described.

#### **Theory of Measurement**

17

### Andreas Gerster

Andreas Gerster received his Diplom-Physiker from the University of Stuttgart

in 1996 and joined HP the same year. An engineer in the HP Böblingen Instrument Division optical standards laboratory, he is responsible for calibration tool development and uncertainty analysis. He is a member of DPG (Physical Society of Germany). Andreas is married, has a daughter, and enjoys sailing and hiking. Measurement has long been one of the bases of technical, economical, and even political development and success. In the old Egyptian culture, surveying and trigonometry were important contributors to their prosperity. Religious and political leaders in these times founded their power on, among other things, the measurement of times and rotary motions, which allowed them to predict solar and lunar eclipses as well as the dates of the flood season of the Nile river. Later in history, weights and length measurements were fundamental to a variety of trading activities and to scientific progress. Improvements in measurement techniques, for example, allowed Keppler to set up his astronomical laws. Keppler used the measurement results of his teacher Tycho Brahe, who determined the orbits of the planets in the solar system with an unprecedented accuracy of two arc minutes.<sup>1</sup> Because of the strong impact of a homogenous system of measurements, all metrologic activities even today are controlled by governmental authorities in all developed countries.

Let us consider first the measurement itself. Measurement is the process of determining the value of a certain property of a physical system. The only possibility for making such a determination is to compare the unknown property with another system for which the value of the property in question is known. For example, in a length measurement, one compares a certain distance to the length of a ruler by counting how often the ruler fits into this distance. But what do you use as a ruler to solve such a measurement problem? The solution is a mathematical one: one defines a set of axiomatic rulers and deduces the practical rulers from this set.

At first, rulers were derived from human properties. Some of the units used today still reflect these rulers, such as feet, miles (in Latin, mile passuum = 1000 double steps), cubits (the length of the forearm), or seconds (the time between two heartbeats is about one second). As one can imagine, in the beginning these axiomatic rulers were anything but general or homogenous—for example, different people have different feet. Only a few hundred years ago, every Freie Reichsstadt (free city) in the German empire had its own length and mass definitions. The county of Baden had 112 different cubits at the beginning of the nineteenth century, and the city of Frankfurt had 14 different mass units.<sup>2</sup> In some cities the old axiomatic ruler was mounted at the city hall near the marketplace and can still be visited today.

With the beginning of positivism, about the time of the revolution in France, people were looking for absolute types of rulers that could make it easier to compare different measurements at different locations. Thus, in 1790, the meter was defined in Paris to be 1/40000000 of the length of the earth meridian through Paris. Because such a measurement is difficult to carry out, a physical artifact was made out of a special alloy, and the standard meter was born. This procedure was established by the international treaty of the meter in 1875, and although the

unit definitions have changed, the contract is still valid today.

Related to this search for suitable axiomatic rulers is the question of how many different rulers are really necessary to deduce all practical units. Among others, F. Gauss delivered valuable contributions to the answer. He proposed a system consisting of only three units: mass, time and length. All other mechanical and electrical and therefore optical units could be deduced. As Lord Kelvin showed in 1851, the temperature is also directly related to mechanical units. Therefore, along with the meter, two other axiomatic rulers were defined. Mass was defined by the international kilogram artifact which was intended to have the mass of one cubic decimeter of pure water at 4°C (in fact it was about 0.0028 g too heavy). The definition of time finally was related to the duration of a certain (astronomical) day of the year 1900.

For various reasons, these definitions were not considered suitable anymore in the second half of the 20th century, and metrologists tried to find natural physical constants as bases for the definition of the axiomatic units. At first the time unit (second) and the length unit (meter) were defined in terms of atomic processes. The meter was related to the wavelength of the light emitted from krypton atoms due to certain electronic transitions. In the case of the time unit, a type of cesium oscillator was chosen. The second was defined by 9,192,631,770 cycles of the radiation emitted by electronic transitions between two hyperfine levels of the ground state of cesium 133.

These new definitions of the axiomatic units had a lot of advantages over the old ones. The units of time and length were now related to natural physical constants. This means that everybody in the world can reproduce these units without having to use any artifacts and the units will be the same at any time in any place.

For practical reasons, more units were added to the base units of the Système International d'Unités, or International System of Units (SI). Presently there are seven base units, two supplementary units, and 19 derived units in the SI. The base units are listed in **Table I**. There is no physical necessity for the selection of a certain set of base units, but only practical reasons. In fact, considering the definitions, only three of the base units—the second, kelvin, and kilogram—are independent, and even the kelvin can be derived from mechanical units.

| Table I                                                                        |                 |                                                                                                                                                                        |  |

|--------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Definitions of the Seven Base Units of the Système International d'Unités (SI) |                 |                                                                                                                                                                        |  |

| Unit                                                                           | Name and Symbol | Definition                                                                                                                                                             |  |

| Length                                                                         | meter (m)       | One meter is now defined as the distance that light travels in vacuum during a time interval of 1/299792458 second.                                                    |  |

| Mass                                                                           | kilogram (kg)   | The kilogram is defined by the mass of the international kilogram artifact in Sèvres, France.                                                                          |  |

| Time                                                                           | second (s)      | A second is defined by 9,192,631,770 cycles of the radiation emitted by the elec-<br>tronic transition between two hyperfine levels of the ground state of cesium 133. |  |

| Electrical<br>Current                                                          | ampere (A)      | An ampere is defined as the electrical current producing a force of $2 \times 10^{-7}$ newtons per meter of length between two wires of infinite length.               |  |

| Temperature                                                                    | kelvin (K)      | A kelvin is defined as 1/273.16 of the temperature of the triple point of water.                                                                                       |  |

| Luminous<br>Intensity                                                          | candela (cd)    | A candela is defined as the luminous intensity of a source that emits radiation of $540 \times 10^{12}$ hertz with an intensity of 1/683 watt per steradian.           |  |

| Amount of<br>Substance                                                         | mole (m)        | One mole is defined as the amount of substance in a system that contains as many elementary items as there are atoms in 0.012 kg of carbon 12.                         |  |

Nevertheless, some small distortions remain. Of course, all measurements are influenced by the definitions of the axiomatic units, and so the values of the fundamental constants in the physical view of the world, such as the velocity of light c, the atomic fine structure constant a, Plank's constant h, Klitzing's constant R, and the charge of the electron e, have to be changed whenever improvements in measurement accuracy can be achieved.

This has led to the idea of relating the axiomatic units directly to these fundamental constants of nature.<sup>3</sup> In this case the values of the fundamental constants don't change anymore. The first definition that was directly related to such a fundamental constant of nature was the meter. In 1983 the best known measurement value for the velocity of light c was fixed. Now, instead of changing the value for c whenever a better realization of the meter is achieved, the meter is defined by the fixed value for c. One meter is now defined as the distance that light travels in a vacuum during a time interval of 1/299792458 second. The next important step in this direction could be to hold the value e/h constant and define the voltage by the Josephson effect (see the Appendix).

#### **Calibration and Traceability**

According to an international standard, calibration is "the set of operations which establish, under specified conditions, the relationship between the values indicated by the measuring instrument and the corresponding known values of a measurand."<sup>4</sup> In other words, calibration of an instrument ensures the accuracy of the instrument.

Of course, no one can know the "real" value of a measurand. Therefore, it must suffice to have a best approximation of this real value. The quality of the approximation is expressed in terms of the uncertainty that is assigned to the apparatus that delivers the approximation of the real value. For calibration purposes, a measurement always consists of two parts: the value and the assigned measurement uncertainty.

The apparatus representing the real value can be an artifact or another instrument that itself is calibrated against an even better one. In any case, this best approximation to the real value is achieved through the concept of *traceability*. Traceability means that a certain measurement is related by appropriate means to the *definition* of the unit of the measurand under question. In other words, we trust in our measurement because we have defined a unit (which is expressed through a standard, as shown later), and we made our measurement instrument conform with the definition of this unit (within a certain limit of uncertainty).

Thus, the first step for a generally accepted measurement is a definition of the unit in question that is accepted by everybody (or at least by all people who are relevant for our business), and the next step is an apparatus that can *realize* this unit. This apparatus is called a (primary) *standard.* What does such an apparatus look like? It simply builds the definition in the real world. In the case of the second, for example, the *realization* of the unit is given by cesium atoms in a microwave cavity, which is used to control an electrical oscillator. The realization of the second is the most accurate of all units in the SI. Presently, uncertainties of  $3 \times 10^{-15}$  are achieved.<sup>5</sup> The easiest realization is that of the kilogram, which is expressed by the international kilogram artifact of platinum iridium alloy in Sèvres near Paris. The accuracy of this realization is excellent because the artifact *is* the unit, but if the artifact changes, the unit also changes. Unfortunately, the mass of the artifact changes on the order of  $10^{-9}$  kg per year.<sup>5</sup>

#### **Representation and Dissemination**

National laboratories (like PTB in Germany or NIST in the U.S.A.) are responsible for the realization of the units in the framework of the treaty of the meter. Since there can be only one institution responsible for the realization, the national laboratories must disseminate the units to anyone who is interested in accurate measurements. Most of the realizing experiments are rather complicated and sometimes can be maintained for only a short time with an appropriate accuracy. Thus, for the dissemination of the unit, an easy-to-handle *representation* of the unit is used. These representations have values that are traceable to the realizing experiments through transfer measurements. New developments in metrology allow the representation of some units as quantum standards, so in some cases the realization of a unit has a higher uncertainty than its representation. In the Appendix this effect is discussed for the example of electrical units.

Once the representation of a unit is available, the calibration chain can be extended. The representations can be duplicated and distributed to institutions that have a need for such secondary standards. In some cases, a representation can be used directly to calibrate general-purpose bench instruments. In the case of electrical units, the representations are used to calibrate highly sophisticated calibration instruments, which allow fully automatic calibration of a device under test, including the necessary reporting.<sup>6</sup>

Although the calibration chain described above is a very common and the most accepted method of providing traceability, it is only one among others. Another method of providing traceability involves comparing against natural physical constants. A certain property of a physical system is measured with the device under test (DUT) and the reading of the device is compared against the known value of this property. For example, a wavelength measurement instrument can be used to measure the wavelength of the light emitted from a molecule as a result of a certain electronic transition. The reading of the instrument can easily be compared against the listed values for this transition. This method of providing traceability has some advantages. It is not necessary to have in-house standards, which have to be recalibrated regularly, and in principle, the physical constant is available everywhere in the world at all times with a fixed value. However, a fundamental issue is to determine what is considered to be a natural physical constant. Of course there are the well-known fundamental constants: the velocity of light, Planck's constant, the hyperfine constant, the triple point of water, and so forth, but for calibration purposes many more values are used. In literature some rather complicated definitions can be found.<sup>3</sup> We'll try a simple definition here: a natural physical constant is a property of a physical system the value of which either does not change under reasonable environmental conditions or changes only by an amount that is negligible compared to the desired uncertainty of the calibration. Reasonable in this context means moderate temperatures  $(-50 \text{ to } 100^{\circ}\text{C})$ , weak electromagnetic fields (order of milliteslas), and so forth.

Somewhat different from the two methods described above are ratio-type measurements using self-calibrating techniques. An example of this technique will be described in the next section.

#### **Calibration of Optical Instruments**

In this section we describe the calibration procedures and the related traceability concepts of some of the optical measurement instruments produced by HP. In contrast to the calibration of electrical instruments like voltmeters, it is nearly impossible to find turnkey solutions for calibration systems for optical instruments. Because optical fiber communications is a new and developing field, the measurement needs are changing rapidly and often the standardization efforts cannot keep pace.

#### **Calibration of Optical Power Meters**

The basic instrument in optical fiber communications is the optical power meter. Like most commercial power meters used for telecommunications applications, the HP 8153A power meter is based on semiconductor photodiodes. Its main purpose is to measure optical power, so the most important parameter is the optical power accuracy.

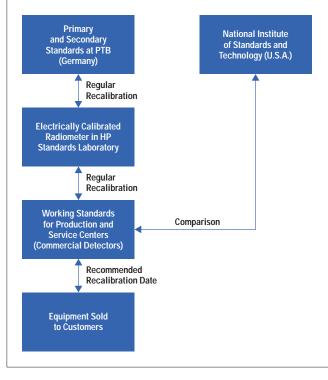

**Figure 1** illustrates the calibration chain for HP's power meters. This is an example of the traceability concept of an unbroken chain of calibrations. It starts with the primary standard at the Physikalisch Technische Bundesanstalt (PTB) in Germany. As discussed in the previous sections, the chain has to start with the definition of the unit. Since we want to measure power, the unit is the watt, which is defined to be  $1W = (1 \text{ m/s})(1 \text{ kg·m/s}^2)$ .

#### Figure 1

The calibration chain for the HP 8153A optical power meter. This is an example of calibration against a national standard (PTB). In addition, the HP working standards are calibrated at NIST in the U.S.A. Thus the calibrations carried out with these working standards are also traceable to the U.S. national standard. HP also participates in worldwide comparisons of working standards. This provides data about the relation between HP's standards and standards of other laboratories in the world.

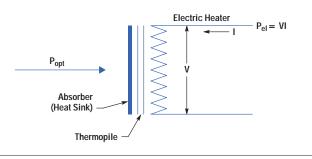

Thus, the optical power must be related to mechanical power. Normally such a primary standard is realized by an electrically calibrated radiometer. The principle is sketched in **Figure 2**. The optical power is absorbed (totally, in the ideal case) and heats up a heat sink. Then the optical power is replaced by an applied electrical power that is controlled so that the heat sink remains at the same temperature as with the optical power applied. (The electrical power is related to mechanical units, as shown in the Appendix.) In this case the dissipated electrical power  $P_{el}$  is equal to the absorbed optical power  $P_{opt}$  and can easily be calculated from the voltage V and the electrical current I:

$$P_{opt} = VI = P_{el}$$

As always, in practice the measurement is much more complicated. Only a few complications are mentioned here; more details can be found in textbooks on radiometry:<sup>7,8</sup>

- Not all light emitted by the source to be measured is absorbed by the detector (a true black body does not exist on earth).

- The heat transfer from the electrical heater is not the same as from the absorbing surface.

- The lead-in wires for the heaters are electrical resistors and therefore also contribute to heating the sink.

For these and other reasons an accurate measurement requires very careful experimental technique. Therefore,

#### Figure 2

Principle of an absolute radiometer (electrically calibrated radiometer). The radiant power is measured by generating an equal heat by electrical power. The heat is measured with the thermopile as an accurate temperature sensor. The optical radiation is chopped to allow control for equal heating of the absorber: the electrical heater is on when the optical beam is switched off by the chopper and vice versa.

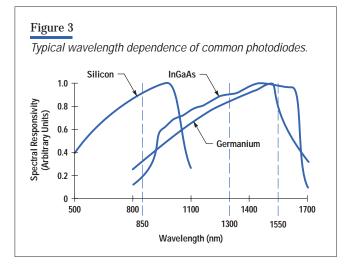

for dissemination, the optical watt is normally transferred to a secondary standard, such as a thermopile. To keep the transfer uncertainty low it is important that this transfer standard have a very flat wavelength dependence, because the next element in the chain—the photodiode can also exhibit a strong wavelength dependence (see **Figure 3**).

Normally, absolute power is calibrated at one reference wavelength, and all other wavelengths are characterized

by their relative responsivities, that is, by the dependence of the electrical output signal on the wavelength of an optical input signal at constant power. Because of all the experimental problems related to traceability from optical to electrical (and therefore mechanical) power, an absolute power uncertainty of 1% is hard to achieve. To keep the transfer uncertainties from PTB to the HP calibration lab as low as possible, HP uses an electrically calibrated radiometer as the first device in its internal calibration chain.

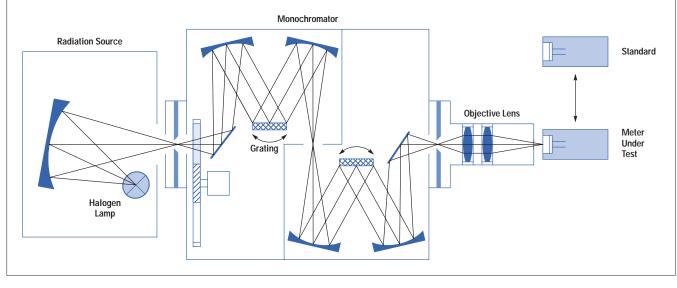

For the selection of a certain wavelength, a white light source in combination with a grating-based monochromator is used (see **Figure 4**). This solution has some advantages over a laser-based method:

- A continuous spectrum is available over a very large wavelength range (from UV to the far IR). Lasers emit light only at discrete lines or the tuning range is limited to a few tens of nanometers.

- A tungsten lamp is a classical light source that exhibits almost no coherence effects.

- The power can be kept relatively flat over a large wavelength range.

- The output beam is only weakly polarized.

#### Figure 4

Calibration setup for absolute power calibration. The monochromator is used to select the wavelength out of the quasicontinuous spectrum of the halogen lamp. The output power as a function of wavelength is first measured with the working standard and then compared with the results of the meter under test. The deviation is used to calculate correction factors that are stored in the nonvolatile memory of the meter.

As always, in practice there are some disadvantages that make a monochromator system an unusual tool:

- A monochromator is an imaging system, that is, external optics are necessary to bring the light into a fiber or onto a large-area detector.

- Available power is rather low compared to the power levels available from telecommunications lasers. Typically 10 μW is achieved in an open-beam application, but the power level that can be coupled into a fiber may be 30 dB less.

- Because a monochromator is a mechanical tool, a wavelength sweep is rather slow. This can give rise to power stability problems.

- Often the optical conditions during calibration are quite different from the usual DUT's application. This leads to higher uncertainties, which must be determined by an uncertainty analysis.

Thus, setting up a monochromator-based calibration system is not without problems. Nevertheless, for absolute power calibration over a range of wavelengths it is the tool of choice. The calibration is carried out by comparing the reading of the DUT at a certain wavelength with the reading of the working standard at this wavelength. The deviation between the two readings yields a correction factor that is written into the nonvolatile memory of the DUT. In the case of the detectors for the HP 8153A power meter the wavelength is swept in steps of 10 nm over the whole wavelength range. The suitable wavelength range depends on the detector technology. For wavelengths between two calibration points, the correction factor is obtained by appropriate interpolation algorithms. After the absolute power calibration is finished, the instrument can deliver correct power readings at any wavelength.

#### **Calibration of Power Linearity**

The procedure described above calibrates only the wavelength axis of the optical power meter. How accurate are power measurements at powers that do not coincide with the power selected for the wavelength calibration? This question is answered by the linearity calibration.

State-of-the-art power meters are capable of measuring powers with a dynamic range as high as 100 dB or more. Ideally, the readings should be accurate at each power level. If one doubles the input power, the reading should also double. A linearity calibration can reveal whether this is really the case. The linearity of the power meter is directly related to the accuracy of relative power measurements such as loss measurements.

There are several reasons for nonlinearity in photodetectors. At powers higher than about 1 mW, the photodiode itself may become nonlinear because of saturation effects. Nonlinearities at lower powers are normally caused by the electronics that evaluate the diode signal. Internal amplifiers are common sources of nonlinearity; their gains must be adjusted properly to avoid discontinuities when switching between power ranges. Analog-to-digital converters can also be the reason for nonlinearities.

In a well-designed power meter the nonlinearities induced by the electronics are very small. Thus, the nonlinearity of a good instrument is near zero, which makes it quite difficult to measure with a small uncertainty. Indeed, often the measurement uncertainty exceeds the nonlinearity.

The linearity calibration of HP power meters is an example of a self-calibration technique.<sup>9,10</sup> The nonlinearity NL at a certain power level  $P_x$  is defined as:

$$\mathrm{NL} = \frac{\mathrm{r_x} - \mathrm{r_{ref}}}{\mathrm{r_{ref}}},$$

where r = D/P is the power meter's response to an optical stimulation, with D being the displayed power and P the incident power. The subscript ref indicates a reference power level, which can be arbitrarily selected. Replacing the responsivity r by D/P, the nonlinearity can be written as:

$$NL = \frac{D_x/P_x}{D_{ref}/P_{ref}} - 1 = \frac{D_x}{D_{ref}} \frac{P_{ref}}{P_x} - 1$$

This can now be compared with the error for a loss measurement. Loss means the ratio between two power levels  $P_1$  and  $P_2$ . Let  $D_1$  and  $D_2$  be the corresponding displayed power levels, and define the real loss  $RL = P_1/P_2$  and the displayed loss  $DL = D_1/D_2$ . The loss error LE is given by the relative difference between RL and DL:

$$LE = \frac{DL - RL}{RL} = \frac{DL}{RL} - 1 = \frac{D_1P_2}{D_2P_1} - 1.$$

It is evident that if one selects  $P_1$  as reference power, the loss error is given by the nonlinearity at  $P_x = P_2$ . If  $P_1$  is different from the reference power  $P_{ref}$  the statement is still valid to a first-order approximation. The bottom line

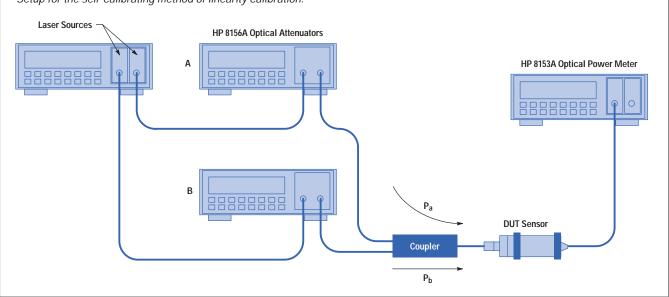

Setup for the self-calibrating method of linearity calibration.

is that in relative power measurements like insertion loss or bit error rate tests, linearity is the important property.

The setup for this self-calibration technique is shown in **Figure 5**. First, attenuator A is used to select a certain power  $P_a$ , which is guided through optical path A to the power meter under test. The corresponding power reading is recorded. Then attenuator A is closed and the same power as before is selected with attenuator B, resulting in a power reading  $P_b$ . Now both attenuators are opened, and the resulting reading  $P_c$  should be nearly the sum of  $P_a$  and  $P_b$  (see **Figure 6**). Any deviation is recorded as nonlinearity. Using the same notation as before, the displayed loss DL is given by:

$$DL = \frac{P_c}{P_a} \approx \frac{P_c}{P_b}.$$

The real loss RL can be calculated by adding the two first readings:

$$\mathrm{RL} = \frac{\mathrm{P}_{\mathrm{a}} + \mathrm{P}_{\mathrm{b}}}{\mathrm{P}_{\mathrm{a}}} \approx \frac{\mathrm{P}_{\mathrm{a}} + \mathrm{P}_{\mathrm{b}}}{\mathrm{P}_{\mathrm{b}}}.$$

Because  $P_a$  and  $P_b$  are selected to be equal, the nonlinearity NL is:

$$\begin{split} \mathrm{NL} &= \frac{\mathrm{DL}}{\mathrm{RL}} = \frac{\mathrm{P_c}}{\mathrm{P_a}} \frac{\mathrm{P_a}}{\mathrm{P_a} + \mathrm{P_b}} \\ &\approx \frac{\mathrm{P_c}}{\mathrm{P_a}} \frac{\mathrm{P_a}}{\mathrm{P_a} + \mathrm{P_a}} = \frac{\mathrm{P_c}}{\mathrm{2P_a}} \end{split}$$

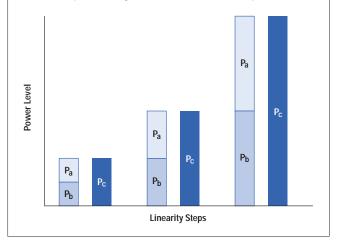

#### Figure 6

The powers selected for the self-calibration procedure. The entire power range is calibrated in 3-dB steps.

The last term on the right side expresses the nonlinearity only in terms of values that are measured by the instrument under test. This means the calibration can be carried out without a standard instrument. Of course, it would also be possible to measure the real loss RL with a standard instrument that was itself calibrated for nonlinearity by a national laboratory. In any case, such a self-calibrating technique has a lot of advantages. There is no standard that must be shipped for recalibration at regular intervals, whose dependencies on external influences and aging contribute to the uncertainty of the calibration process, and that could be damaged, yielding erroneous calibrations.

#### **Calibration of Laser Sources**

The last example will deal with calibration against natural physical constants and will be used to make some remarks about the determination of uncertainties. Having dealt with optical power sensors we will now focus on sources.

The most commonly used source in optical communications is the semiconductor laser diode. Only a few years ago, the exact wavelength emitted by the lasers was not so important. Three wavelength windows were widely used: around 850 nm, 1300 nm, and 1550 nm. 850 nm was chosen pragmatically; the first available laser diodes emitted at this wavelength. At 1300 nm, fiber pulse broadening is minimal in standard fibers, allowing the highest bandwidth, and at 1550 nm, fiber loss is minimum. As long as a fiber link or network operated at only one wavelength, as was mainly the case in recent years, and all its components exhibited only weak wavelength dependence, the exact wavelength was not of great interest. An accuracy of about 1 nm or even worse was good enough. Indeed, a lot of laser sources are specified with an accuracy of  $\pm 10$  nm.

The situation changed completely with the advent of wavelength-division multiplexing (WDM). This means that several different wavelengths (i.e., colors) are transmitted over one link at the same time, allowing an increase in bandwidth without burying new fibers. Since the single channels are separated by only 1.6 or 0.8 nm, one can easily imagine that wavelength accuracy becomes very important. Today wavelength accuracy on the order of a few picometers is required for WDM applications. The task of providing such wavelength accuracy for tunable laser sources like the HP 8168 Series is quite challenging.

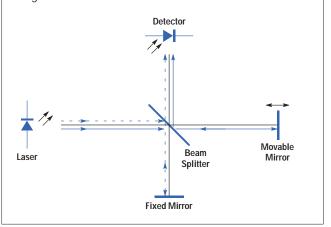

#### Figure 7

Principle of the Michelson interferometer. A coherent beam is split by a beam splitter and directed into two different arms. After reflection at the fixed and movable mirrors, the superposition of the two beams is detected by a photodetector. Because the two beams are coherent, the superposition will give rise to an interference term in the intensity sum. Thus, moving the movable mirror will cause the intensity detected by the detector to exhibit minima and maxima. The distance between two maxima corresponds to a displacement of  $\lambda/2$  of the movable mirror, where  $\lambda$  is the wavelength of the laser source. Measuring the necessary displacement to produce, say, ten maxima will allow a direct determination of the wavelength.

The accuracy should be the same over the whole wavelength range. The first question is how wavelength is measured.

First, it should be clear that wavelength means vacuum wavelength, which is effectively the frequency. Unfortunately, the wavelength of light varies under a change of the refractive index of the material it passes through. The tools for measuring nanometer distances are interferometers. Most of the commercially available wavelength meters are based either on the Michelson interferometer or the Fabry-Perot interferometer.<sup>11</sup> We will focus on the Michelson technique here.

The principle of the Michelson interferometer is shown in **Figure 7**. The challenge in the case of the Michelson interferometer is to measure the shift of the movable mirror. The required uncertainty of a few pm cannot, of course, be achieved by mechanical means. Instead, the interference pattern produced by light with a known wavelength is compared to the pattern of the unknown source and by comparison the unknown wavelength can be calculated. The known light source is used here as a natural physical constant. Of course, the wavelength of this source must be independent of external influences. A stabilized He-Ne laser is often used because the central wavelength of its 633-nm transition is well-known and there are several methods of stabilizing the laser wavelength to an accuracy of fractions of 1 pm. Thus, such an interferometer-based wavelength meter is the ideal tool to calibrate a laser source for wavelength accuracy.

As mentioned above, every measurement consists of two parts: the measurement value and the corresponding uncertainty. The uncertainty of a specific measurement is estimated by a detailed uncertainty analysis.<sup>12</sup> As an example, **Table II** shows a fictitious uncertainty calculation for measuring the vacuum wavelength of a laser source with a Michelson interferometer in normal air. As shown, all relevant influences have to be listed and their individual contributions summed. The most difficult part is the

Table II

Example of an Uncertainty Calculation

| Component                                                        | Standard<br>Deviation<br>±                                                                                                                | Uncertainty<br>±                                                                                 |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Internal Influences:<br>Uncertainty of Reference<br>Laser        | $0.08 	imes 10^{-6}$                                                                                                                      | $0.15 	imes 10^{-6}$                                                                             |

| Alignment, Diffraction<br>Fringe Counting<br>Resolution          | $1.1 	imes 10^{-6}$<br>$0.5 	imes 10^{-6}$                                                                                                | $\begin{array}{c} 2.2 \times 10^{-6} \\ 1.0 \times 10^{-6} \end{array}$                          |

| Total 1                                                          | <b>1.2</b> ×10 <sup>-6</sup>                                                                                                              | $2.4 \times 10^{-6}$                                                                             |

| Atmospheric Influences:<br>Content of Carbon-<br>dioxide (1/ppm) | $0.17 	imes 10^{-9}$                                                                                                                      | $0.34 	imes 10^{-9}$                                                                             |

| Relative Humidity<br>Air Pressure<br>Temperature<br>Total 2      | $\begin{array}{c} 1.95 \times 10^{-9} \\ 2.88 \times 10^{-8} \\ 5.71 \times 10^{-9} \\ \textbf{2.94} \times \textbf{10^{-8}} \end{array}$ | $4.00 \times 10^{-9}$<br>$5.76 \times 10^{-8}$<br>$1.14 \times 10^{-8}$<br>$5.88 \times 10^{-8}$ |

| Uncertainty of Edlén<br>Equation                                 | 1.15×10 <sup>-8</sup>                                                                                                                     | 2.30×10 <sup>-8</sup>                                                                            |

| Extension of Wavelength<br>Limits                                | 1.15×10 <sup>-8</sup>                                                                                                                     | 2.30×10 <sup>-8</sup>                                                                            |

| Influences from Source<br>Under Test                             | 3.11×10 <sup>-10</sup>                                                                                                                    | 5.38×10 <sup>-10</sup>                                                                           |

| Total                                                            | <b>1.2</b> ×10 <sup>-6</sup>                                                                                                              | $2.4 \times 10^{-6}$                                                                             |

determination of the values of the contributions. For statistical reasons, the sum is gained by a root-sum-square algorithm. This uncertainty calculation is the most important part of a calibration. The quality of the instrument to be calibrated is determined by the results of this analysis. In the case of a calibration process in a production environment, the specifications for all instruments sold depend on it.

In **Table II**, the uncertainty caused by influences from the source under test is considered to be rectangularly distributed. Thus, the standard deviation is  $1/\sqrt{3}$  times the uncertainty. In all other cases the standard deviation is known and a Gaussian distribution can be assumed. This leads to an uncertainty of two times the standard deviation at a confidence level of 95%. The Edlén equation is an analytical expression that describes the dependence of the refractive index of air on environmental conditions like temperature and humidity.

#### Wavelength or Frequency?

Finally, we'll consider the relation between wavelength and frequency. Because the definition of the meter is related to the definition of time and therefore frequency (and moreover, the frequency of light is invariant under all external conditions) it seems that it might be better to measure the frequency of the light emitted by a laser source rather than its wavelength.

It is now possible to measure a frequency of around 100 THz ( $10^{14}$  Hz). About two years ago, researchers from PTB succeeded in coupling the frequency of a laser emitting at 657 nm directly to the primary time standard (a Cesium clock as mentioned above) which oscillates at 9 GHz.<sup>13</sup> This coupled laser is a realization of a vacuum wavelength standard (and therefore a meter standard) which currently has an unequaled uncertainty of  $9 \times 10^{-13}$ .

Unfortunately, this method of directly measuring the frequency of light is very difficult, time-consuming, and expensive, so only a few laboratories in the world are able to carry it out. Thus, for the time being, wavelength will remain the parameter to be calibrated instead of frequency. Nevertheless, this is a good example of how lively the science of metrology is today.

#### Acknowledgments

I would like to thank my colleagues Horst Schweikardt and Christian Hentschel for their fruitful discussions.

#### References

1. W.R. Fuchs, *Bevor die Erde sich bewegte*, Deutsche Verlags Anstalt, 1975

2. W. Trapp, Kleines Handbuch der Masse, Zahlen, Gewichte und der Zeitrechnung, Bechternuenz Verlag, Augsburg, 1996.

3. B.W. Petley, *The Fundamental Physical Constants and the Frontier of Measurement*, Adam Hilger, Ltd., 1995.

4. Calibration of Fiber-Optic Power Meters, IEC Standard 1315.

5. S. Ghezali, cited by E.O. Göbel, "Quantennormale im SI Einheitensystem," *Physikalische Blätter*, Vol. 53, 1997, p. 217.

6. *Calibration: Philosophy and Practice*, Fluke Corporation, 1994.

7. W. Budde, *Physical Detectors of Optical Radiation*, Academic Press, Inc., 1983.

8. W. Erb, Editor, *Leitfaden der Spektroradiometrie*, Springer Verlag, 1989.

9. C.L. Sanders, "A photocell linearity tester," *Applied Optics*, Vol. 1, 1962, p. 207.

10. K.D. Stock (PTB Braunschweig), "Calibration of fiber optical power meters at PTB," *Proceedings of the International Conference on Optical Radiometry*, London, 1988.

11. *Fiber Optics Handbook*, Hewlett-Packard Company, part no. 5952-9654.

12. Guide to the Expression of Uncertainty in Measurement, International Organization for Standardization (ISO), 1993.

13. H. Schnatz, B. Lipphardt, J. Helmcke, F. Riehle, and G. Zinner, "Messung der Frequenz Sichtbarer Strahlung," *Physikalische Blätter*, Vol. 51, 1995, p. 922.

#### Bibliography

1. D. Derickson, *Fiber Optic Test and Measurement*, Prentice Hall PTR, 1998.

## **Appendix: Realization of Electrical Units**

A lot of measurements today are carried out using electrical sensors. Therefore, it is important to know how the electrical units are realized and related to the mechanical quantities in the Système International d'Unités (SI). In optical fiber communication all power measurements use electrical sensors.

Historically, the electrical units are represented by the ampere among the seven SI base units. Unfortunately, it is not easy to build an experiment that realizes the definition of the ampere in the SI (see Table I on page 19). It is disseminated using standards for voltage and resistance using Ohm's law. Nevertheless, there is a realization for the ampere (see the current balance in **Figure 1**).

A coil carrying a current I exhibits a force F in the axial direction (z direction) if it is placed in an external inhomogeneous magnetic field H (F  $\propto \partial H(z)/\partial z$ ). The force is measured by compensating the force with an appropriate mass on a balance. The uncertainty of such a realization is around 10<sup>-6</sup>, the least accurate realization of all SI base units.

A similar principle is used for the realization of the volt, which is not a base but a derived SI unit. For realization one uses the following relation which can be derived from the SI definition of the voltage V (1 volt = 1 watt /ampere):

$W = V \cdot I \cdot t$

#### Figure 1

Principle of a current balance. The force experienced by the inner coil is compensated by an appropriate mass on the balance.

or

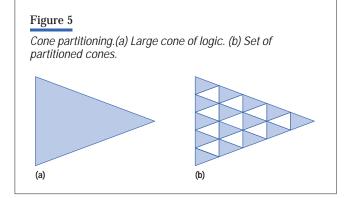

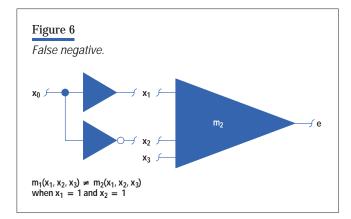

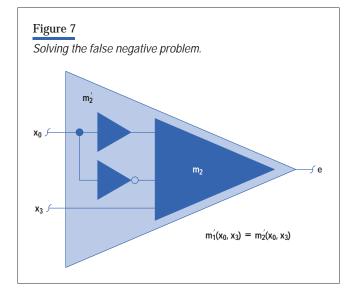

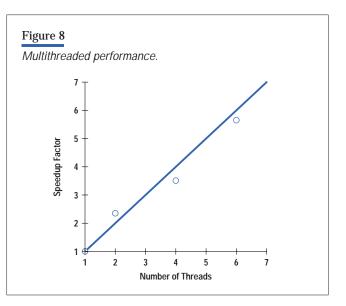

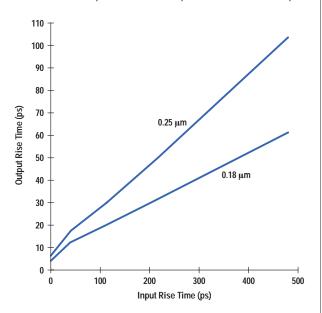

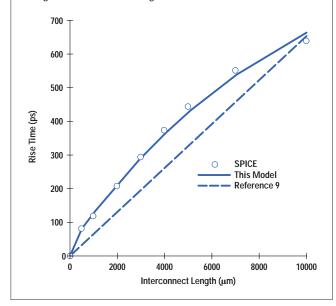

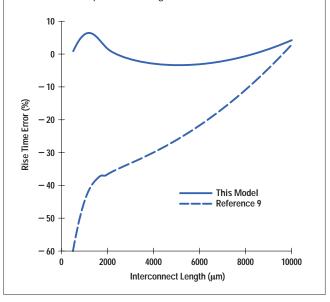

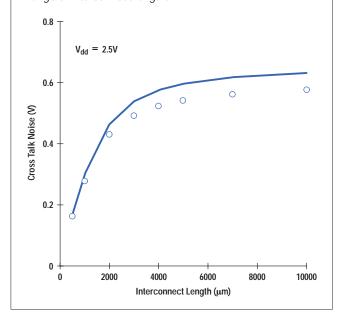

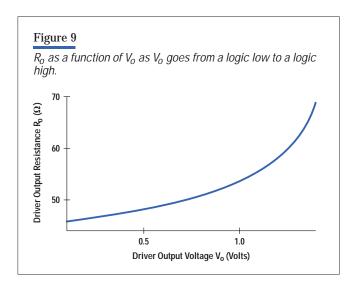

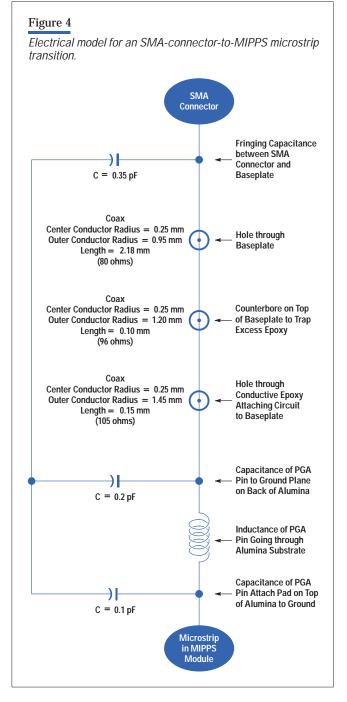

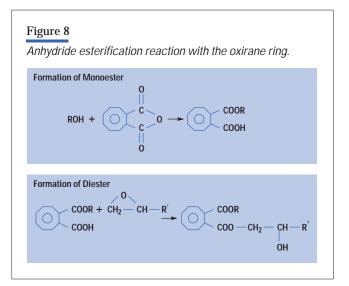

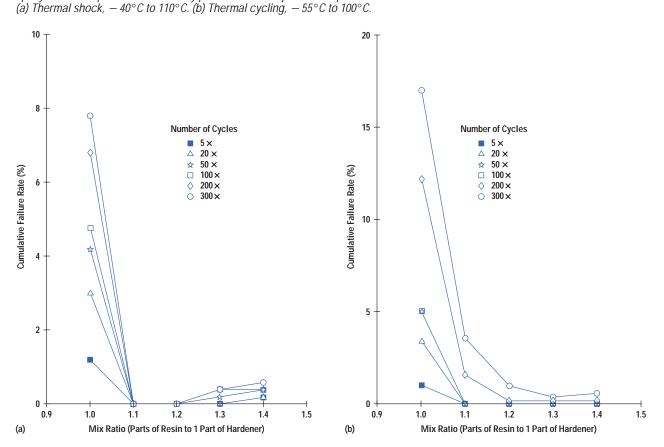

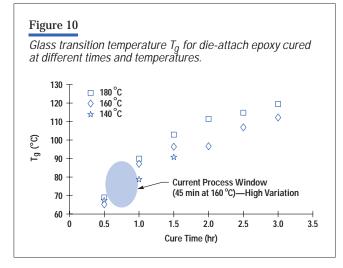

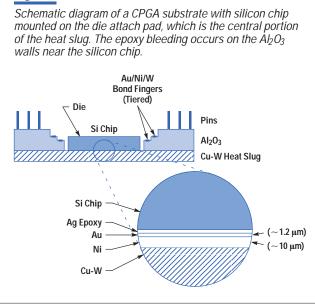

$$V = \frac{W}{I \cdot t}$$